2024年8月28日~8月30日にハイブリッド開催(開催地は鳥羽シーサイドホテル)されたDAシンポジウム2024にて、以下の発表を行いました(発表日は上3件が8月28日, 続く5件が8月29日、最後の1件が8月30日)。

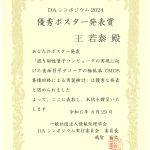

王 若泰, 佐藤 高史, 粟野 皓光, “誤り耐性量子コンピュータの実現に向けた表面符号デコーダの極低温 CMOS 集積回路による実装検討”, DAシンポジウム2024, 2B-3, 2024年8月.

Zhang Mingtao, Cheng Quan, 粟野 皓光, Lin Longyang, 橋本 昌宜, “Squeezing 8-bit Multiplier Energy with Input Segmentation in DNN Inference Accelerators”, DAシンポジウム2024, 3A-2, 2024年8月.

川上 拓真, 佐藤 高史, 粟野 皓光, “4.2K での 65nm バルク pMOS トランジスタにおけるランダムテレグラフノイズの評価”, DAシンポジウム2024, 4A-2, 2024年8月.

田中 知成, 上薗 巧, 末永 幸平, 橋本 昌宜, “制御フロー仕様から生成したペトリネットに基づくハードウェア誤動作検出手法”, DAシンポジウム2024, 5B-3, 2024年8月.

陳 振哲, 佐藤 高史, “Dancing LinksとXアルゴリズムでナンプレ求解”, DAシンポジウム2024, 8A-2, 2024年8月.

宇都宮 優巳, 村田 寛也, 佐藤 高史, 粟野 皓光, “180nmプロセス試作チップに基づくトランジスタのばらつきを利用したハードウェアESNの検討”, DAシンポジウム2024, 8B-2, 2024年8月.

河野智奈武, 宮村信, 白旭, 阪本利司, 越智裕之, 橋本昌宜, “メモリスタクロスバーへのニューラルネットワーク書き込みにおける write-verify 回数削減手法の検討”, DAシンポジウム2024, 9B-3, 2024年8月.

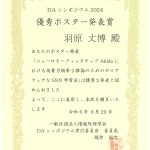

羽原 丈博, 佐藤 高史, 粟野 皓光, “ニューロモーフィックチップAkidaにおける高電力効率な推論のためのゼロアウェアなSNN学習法”, DAシンポジウム2024, 10B-1, 2024年8月.

Xinyi Guo, Geguang Miao, Shinichi Nishizawa, Shinji Kimura, Takashi Sato, “Optimizing Prime Factorization Scalability via Quantum Annealing with Analytical and Pattern-Based Variable Reduction under Partial Constraints”, DAシンポジウム2024, 12A-1, 2024年8月.

また1件目及び8件目の発表について優秀ポスター発表賞を受賞しました.

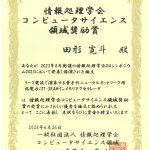

また昨年度の発表に対して情報処理学会CS領域奨励賞及び優秀発表賞が授与されました(8月28日)。